## Intel® Itanium® Architecture Update

5th October, 2006 Dr. Feixiong Liu Technical Manager for HP TSG Intel EMEA

Copyright © 2006 Intel Corporation

### Agenda

Itanium® Processor Family Roadmap

Itanium® 2 Processor update & technology highlights

Montecito Processor Performance update

Itanium<sup>®</sup> 2 Processor Vs Power 5+ competitive position

Itanium® 2 Processor Vs X86 Positioning

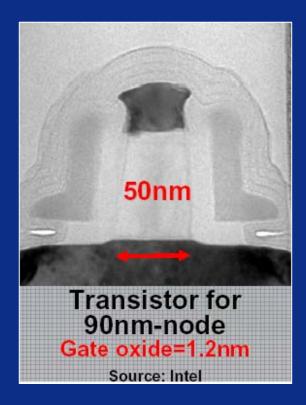

# How many transistors in the next generation of Intel® Itanium® 2 processors?

#### 1.72 billion transistors

# How big is the transistor in the next generation Itanium® Processor?

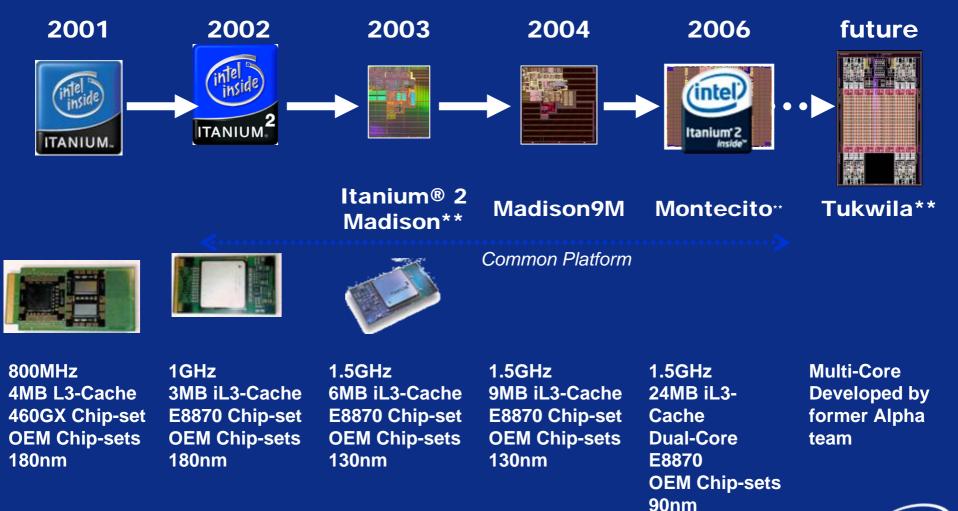

## Intel<sup>®</sup> Itanium<sup>®</sup> Processor Family

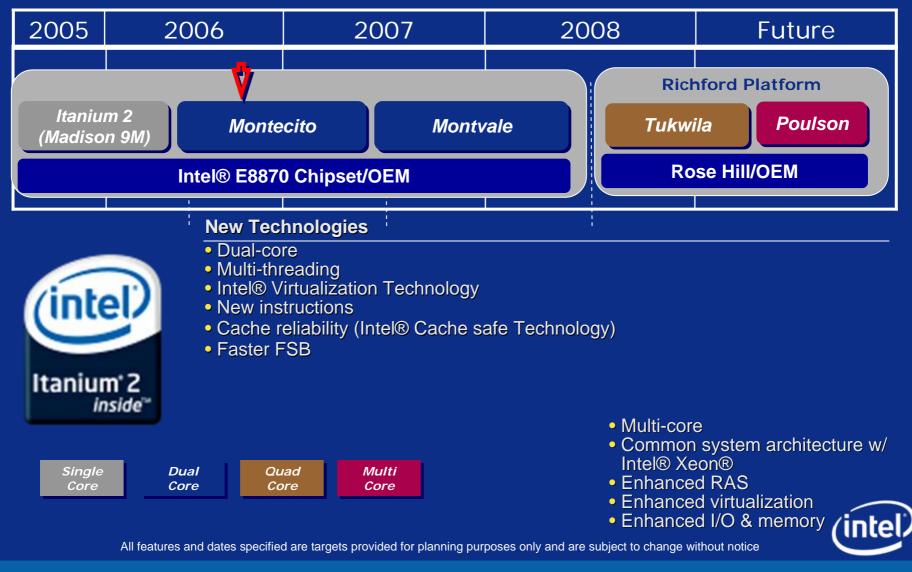

All features and dates specified are targets provided for planning purposes only and are subject to change.

Rev i1.1\_4718844

## Intel® Itanium® Processor Family Roadmap Update

#### Agenda

Itanium<sup>®</sup> Processor Family Roadmap Itanium<sup>®</sup> 2 Processor update & technology highlights Montecito Processor Performance update 64-bit Windows and SQL Server 2005 on Itanium® processor Itanium<sup>®</sup> 2 Processor Vs Power 5+ competitive position Itanium<sup>®</sup> 2 Processor Vs X86 Positioning

### Introducing

#### Dual core Intel® Itanium® 2 Processor 9000 Series processor

#### New features for performance

**Dual-Core**

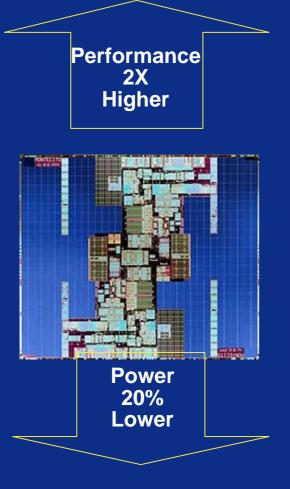

24MB on-die level 3 cache + new 1MB L2 D-cache Intel® Hyper-Threading Technology Intel® Virtualization Technology Intel® Cache Safe Technology 104W, 2.5x performance/watt improvement PCI-Express & DDR2

#### Plus...

Based on EPIC architecture Scalability: Systems scaling to 32P, 64P, and beyond Mainframe class reliability features First 1.72 billion transistors processor

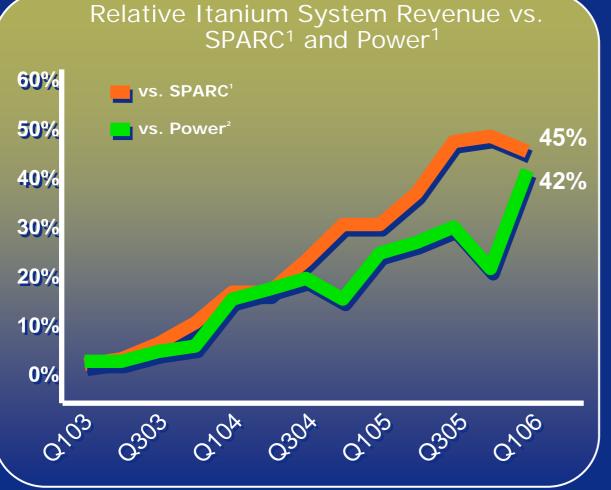

## Itanium<sup>®</sup> Momentum Continues

**Intel Confidential**

Rev i1.1\_4718844 20<sup>th</sup> July 2006 Intel® Itanium® Architecture Update

9

**Rapid Growth in System Revenue**

#### **Specific Countries**

|        | versus<br>SPARC <sup>1</sup> | versus<br>Power <sup>2</sup> |

|--------|------------------------------|------------------------------|

| Japan  | 110%                         | 109%                         |

| Korea  | 68%                          | 51%                          |

| PRC    | 55%                          | 43%                          |

| Russia | 352%                         | 97%                          |

1: SPARC Includes: SPARC I, SPARC II, SPARC III, SPARC IV, SPARC 64 and SPARC 64 V; 2: POWER Includes: Power RS64 II, Power RS64 III, Power RS64 III, Power 3, Power 4, Power 5, and PowerPC Source: IDC Q1'06 WW Quarterly Server Tracker Other names and brands may be claimed as the property of others

#### Intel<sup>®</sup> Itanium<sup>®</sup> Architecture Processors

|                 | Madison9M     | tanium <sup>2</sup><br>inside<br>Montecito |  |  |

|-----------------|---------------|--------------------------------------------|--|--|

| Technology      | 130nm         | 90nm                                       |  |  |

| Number of cores | 1             | 2                                          |  |  |

| Clockrate       | 1600MHz       | 1600MHz                                    |  |  |

| - INT Units     | 6             | 6                                          |  |  |

| - MM Units      | 6             | 6                                          |  |  |

| - FP Units      | 2 (*,+)       | 2 (*,+)                                    |  |  |

| - ADDR Units    | 2L+2S or 4L   | 2L+2S or 4L                                |  |  |

| L1-Caches (I/D) | 16/16KB       | 16/16KB                                    |  |  |

| L2-Cache (I/D)  | 256KB Unified | 1MB/256KB                                  |  |  |

| L3-Cache        | 9MB           | 24MB on die                                |  |  |

| System Bus      | 6.4GB/s       | 8.5GB/s                                    |  |  |

| - Clockrate     | 400MHz        | 533MHz                                     |  |  |

| - Width         | 128 bit       | 128 bit                                    |  |  |

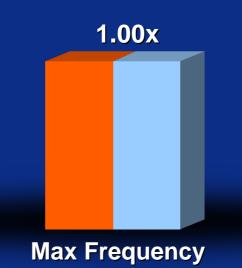

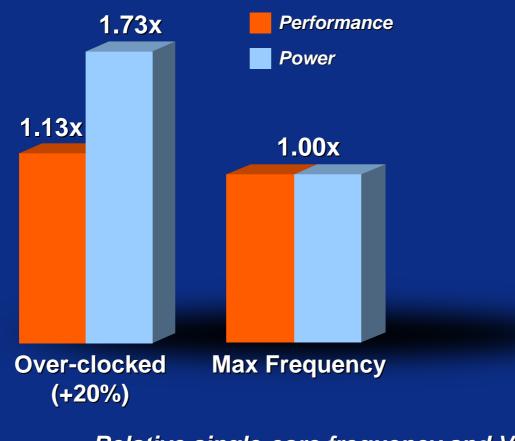

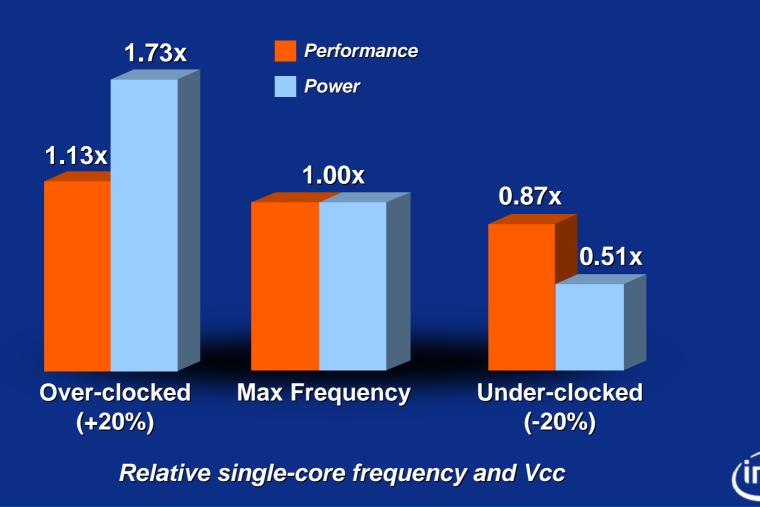

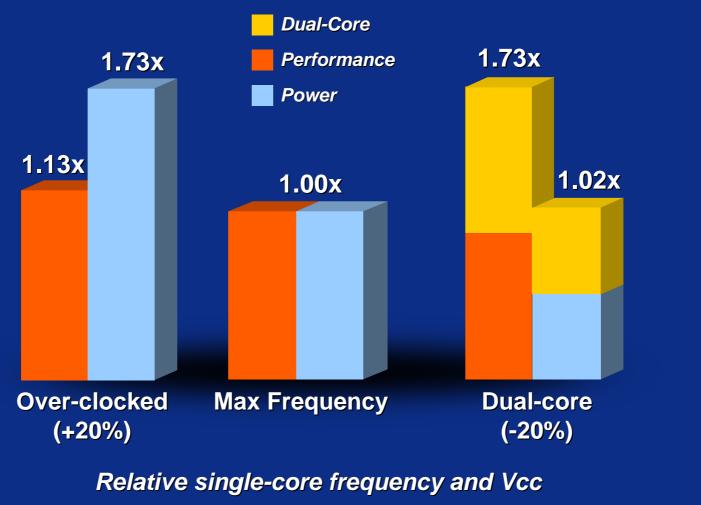

## Why Multi-Core?

Relative single-core frequency and Vcc

12 20th July 2006 Intel® Itanium® Architecture Update

Rev i1.1\_4718844

## **Over-clocking**

(intel)

Relative single-core frequency and Vcc

## **Under-clocking**

Rev i1.1\_4718844

## Multi-Core = Energy Efficient Performance

Rev i1.1\_4718844

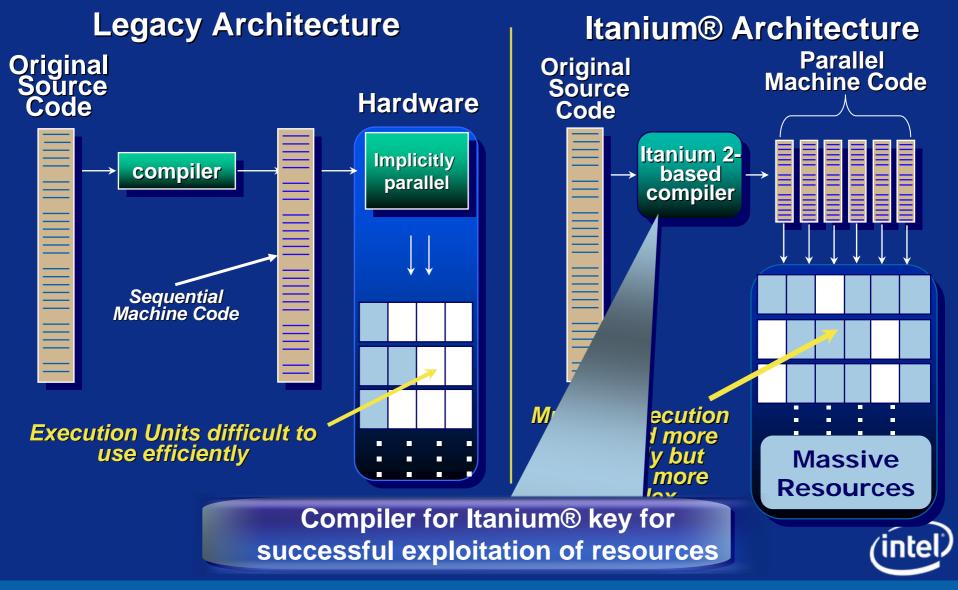

## **Out-of-order versus Explicit Parallelism**

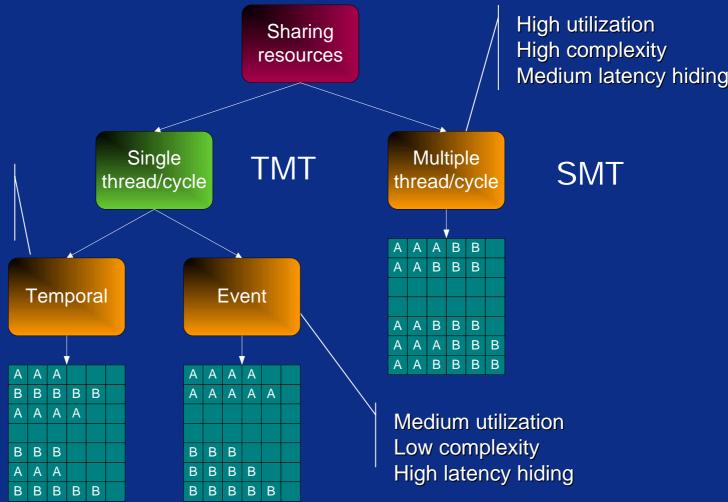

## Multi-Threading Approaches

Medium utilization Low complexity Medium latency hiding

"Event" for the core and "Multiple" for the caches

Intel Confidential

Rev i1.1\_4718844

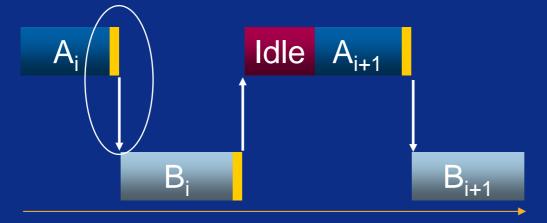

## Montecito Thread Switching

- Switch events

- L3 miss/return

- Instruction, Data or HPW access

- Time slice expiration

- Low power state entered/exited

- Switch hint execution (hint@pause instruction retired)

- ALAT invalidation

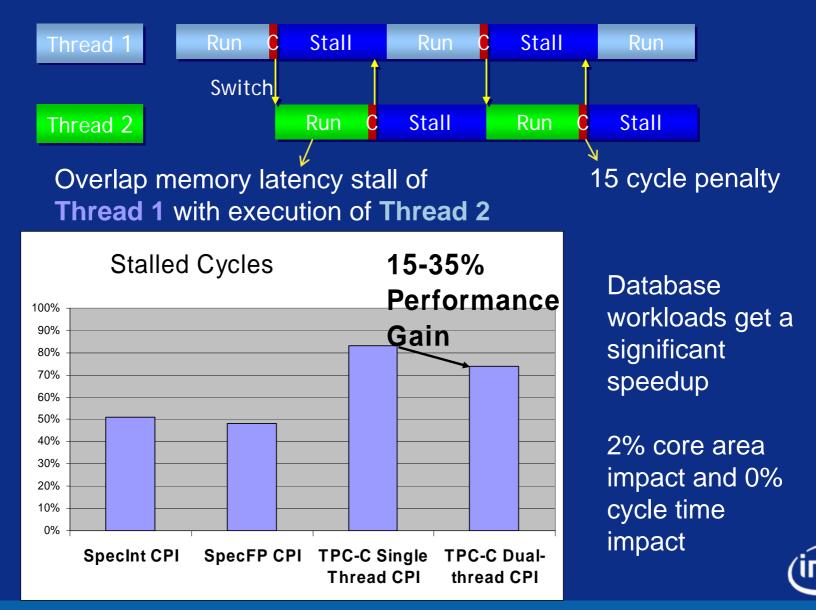

## Montecito Multi-threading

**Montecito Multi-threaded Execution**

Multi-threading decreases stalls and increase performance

## **Temporal Multi-Threading**

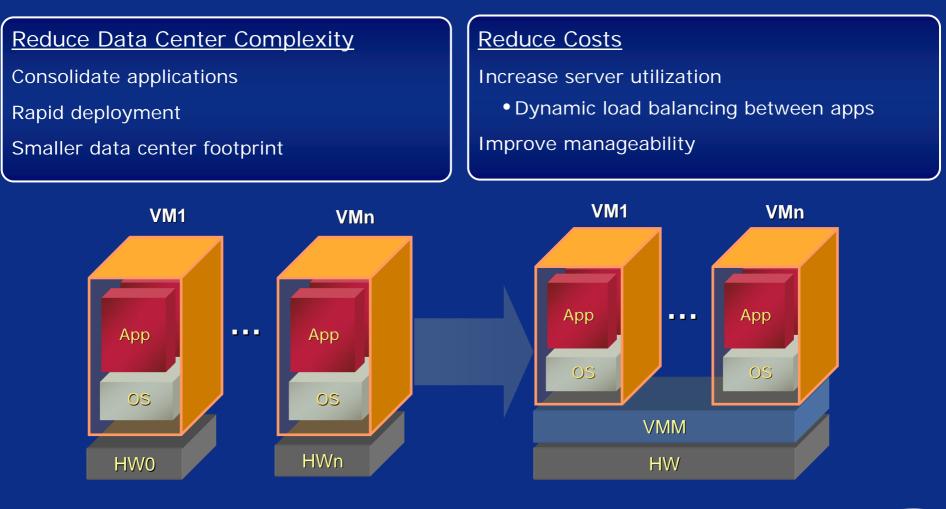

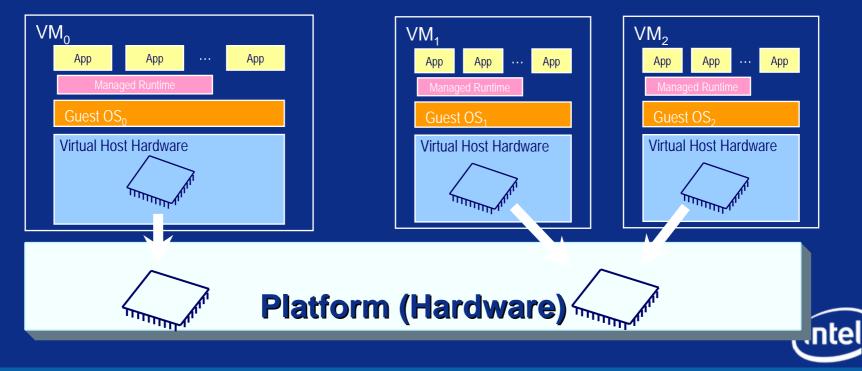

#### Itanium<sup>®</sup> 2 Architecture Virtualization Benefits

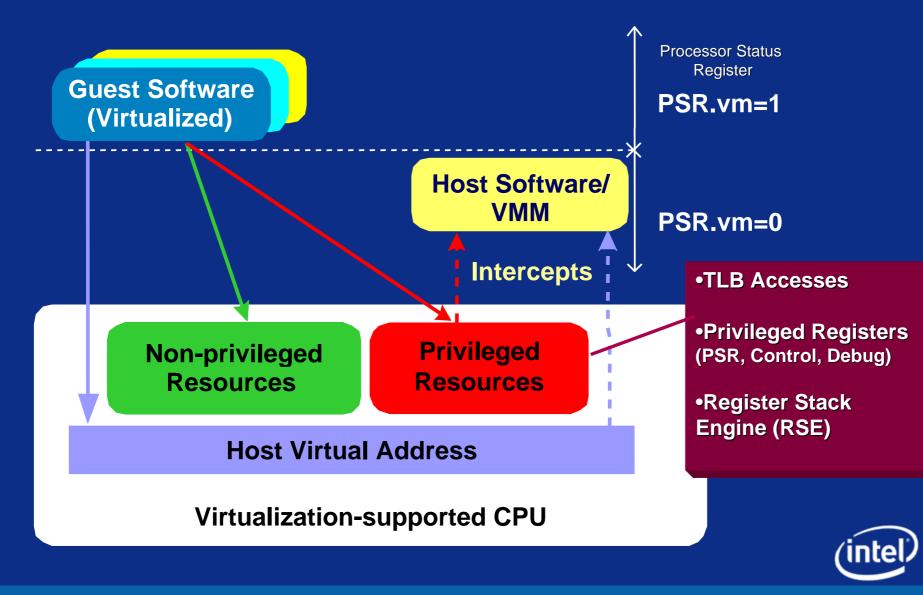

#### Hardware Assisted Virtualization on Itanium <sup>®</sup> Architecture

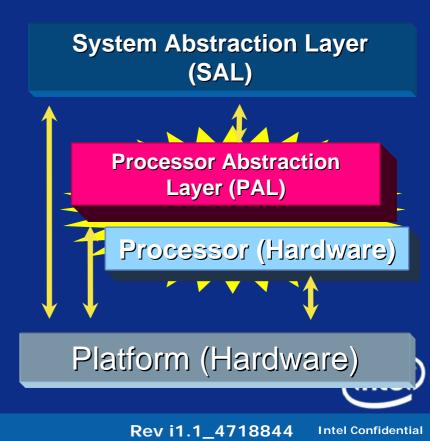

Itanium<sup>®</sup> Virtualization Architecture

• Combination of new processor hardware and PAL firmware functionality

- PAL provides a uniform programming interface across different processor generations

- Extended the PAL to provide run-time services for VMM to manage application and system register state

## Itanium<sup>®</sup> Virtualization Overview

Rev i1.1\_4718844

## **Shared and Dedicated VMs**

#### **Dedicated Policy**

- OS solely owns a set of processor resources

- Reduce conditions that cause intercepts

- (Disable controls)

#### Shared Policy

- Processors are shared across multiple virtual images

- Avoid intercepts by using shadowed processor state

- (Accelerations)

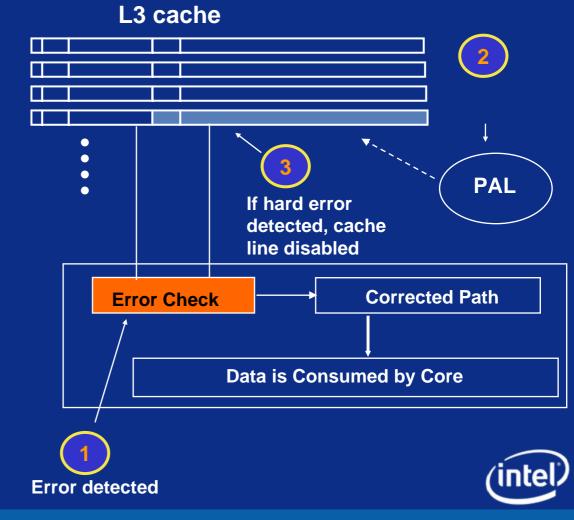

# Advanced Cache Reliability Intel® cache safe Technology

- 1. Cache line access with error detected

- 2. Montecito test for hard error in cache line

- 3. If hard error is detected, cache line is disabled. Processor and system continue normal operation

## **Montecito Processor Error Coverage**

| Structure     | Hardware | Action                                                   |

|---------------|----------|----------------------------------------------------------|

| L1 data cache | Parity   | PAL-correctable                                          |

| L1 tags       | Parity   | PAL-correctable                                          |

| L2 cache data | ECC      | HW-correctable                                           |

| L2 cache tags | ECC      | HW-correctable                                           |

| L3 cache data | ECC      | HW-correctable +<br>Cache Safe® cache reliability        |

| L3 cache tags | ECC      | HW-correctable                                           |

| Register      | Parity   | Recoverable                                              |

| TLB           | Parity   | Recoverable                                              |

| Bus           | ECC      | 1-bit errors HW-correctable,<br>2-bit errors recoverable |

PAL-Correctable and Recoverable errors are dependent upon microarchitectural state

## **Comparing reliability Features**

| Characteristic                                                   | Itanium <sup>®</sup> 2 | IBM*<br>Power* 5 | Intel® Xeon <sup>™</sup><br>MP | Intel®<br>Xeon <sup>™</sup> DP | AMD*<br>Opteron* |

|------------------------------------------------------------------|------------------------|------------------|--------------------------------|--------------------------------|------------------|

| Advanced error detection/ correction/<br>recovery/ logging (MCA) | $\checkmark$           |                  |                                |                                |                  |

| Internal soft error logic check                                  | Montecito              |                  |                                |                                |                  |

| Cache reliability (Pellston)                                     | Montecito              |                  |                                |                                |                  |

| Processor-level lockstep                                         | Montecito              |                  |                                |                                |                  |

| Error recovery on data bus (ECC and retry)                       | $\checkmark$           | $\checkmark$     | $\checkmark$                   |                                |                  |

| Partitioning                                                     | $\checkmark$           | $\checkmark$     | $\checkmark$                   |                                |                  |

| Memory SDEC, retry on double-bit                                 | $\checkmark$           | $\checkmark$     | $\checkmark$                   | $\checkmark$                   |                  |

| Memory scrubbing                                                 | $\checkmark$           | $\checkmark$     | $\checkmark$                   | $\checkmark$                   |                  |

| Memory mirroring and sparing                                     | $\checkmark$           | $\checkmark$     | $\checkmark$                   | $\checkmark$                   |                  |

| Hot Plug I/O (PCI-X, PCI-E) & I/O CRC                            | $\checkmark$           | $\checkmark$     | $\checkmark$                   | $\checkmark$                   | $\checkmark$     |

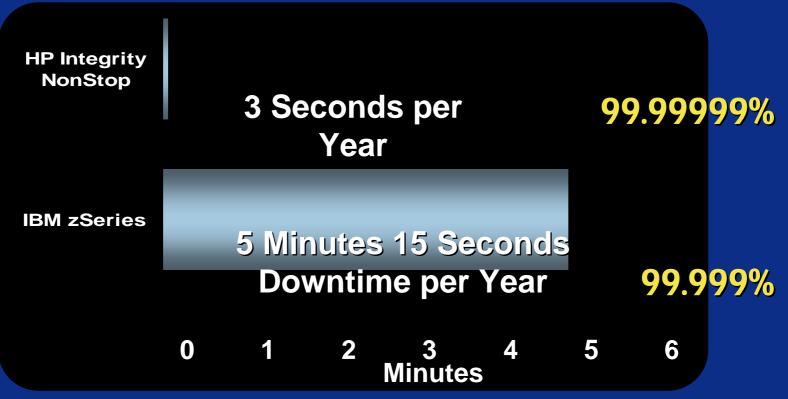

#### Reliability required to replace RISC and mainframes

## **Mission Critical Reliability**

\*Other brands and names are the property of their respective owners.

#### Agenda

Itanium<sup>®</sup> Processor Family Roadmap

Itanium<sup>®</sup> 2 Processor update & technology highlights

Montecito Processor Performance update

Itanium<sup>®</sup> 2 Processor Vs Power 5+ competitive position

Itanium® 2 Processor Vs X86 Positioning

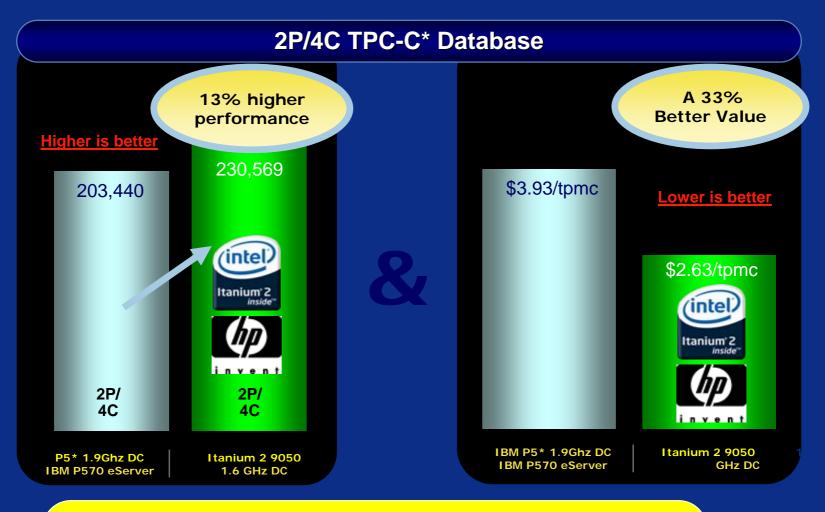

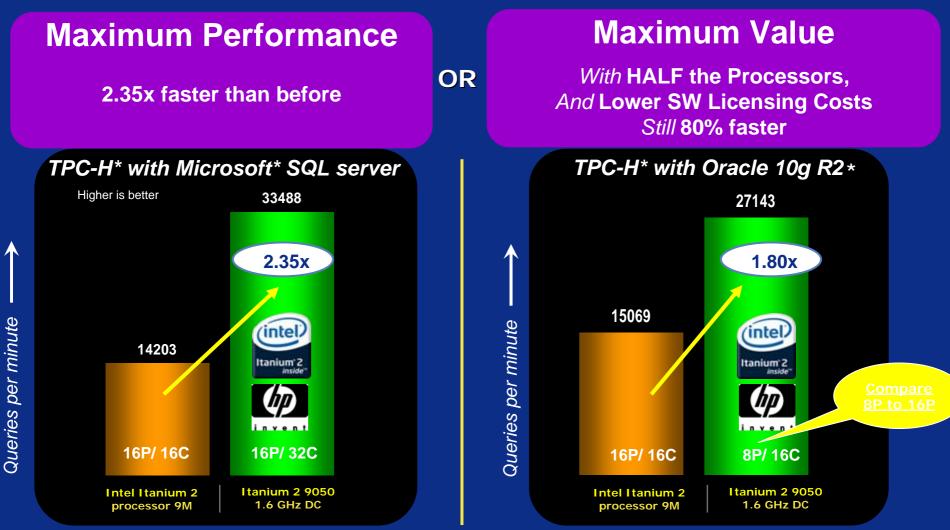

#### **Powerful Database Performance**

#### **Comparison to RISC**

#### **Better Value Compared to RISC based Servers**

Data Source: Published or Submitted results as of August 30th, 2006 (http://www.toc.org Dual Core Itanium® 2 Processor 9050. "p" is a processor or socket and "C" is a core

Dual-Core Intel® Itanium® 2 processor 9000 sequence server

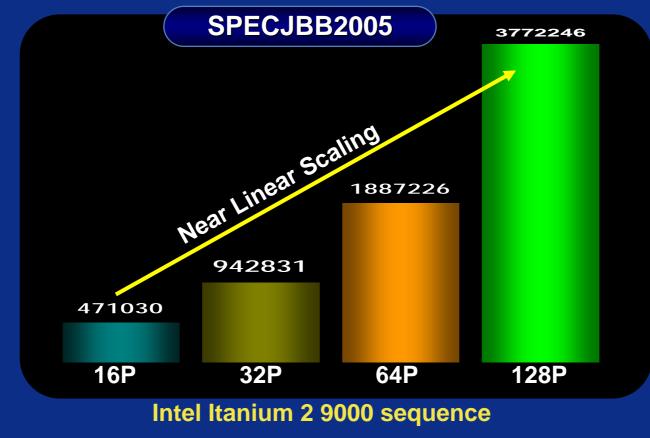

Scaling performance on Java Benchmark

Data Source: Published or Submitted results as of July 18th, 2006. See backup for details Itanium 2 9000 sequence: Dual Core Itanium 2 "Montecito 1.6Ghz" "p" is a processor or socket and "C" is a core

#### **Itanium 2 Platform Shows Excellent scaling**

31 20th July 2006 Intel® Itanium® Architecture Update

Rev i1.1\_4718844

#### **Business Analytics Performance**

1000 GB database

Data Source: Published or Submitted results as of August 30th, 2006 (http://www.tpc.org Dual Core Itanium® 2 Processor 9050. "p" is a processor or socket and "C" is a core

Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of Intel products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. Buyers should consult other sources of information to evaluate the performance of systems or components they are considering purchasing. For more information on performance tests and on the performance of Intel products, visit http://www.intel.com/performance/resources/limits.htm or call (U.S.) 1-800-628-8686 or 1-916-356-3104.

**Intel Confidential**

32 20th July 2006 Intel® Itanium® Architecture Update

Rev i1.1\_4718844

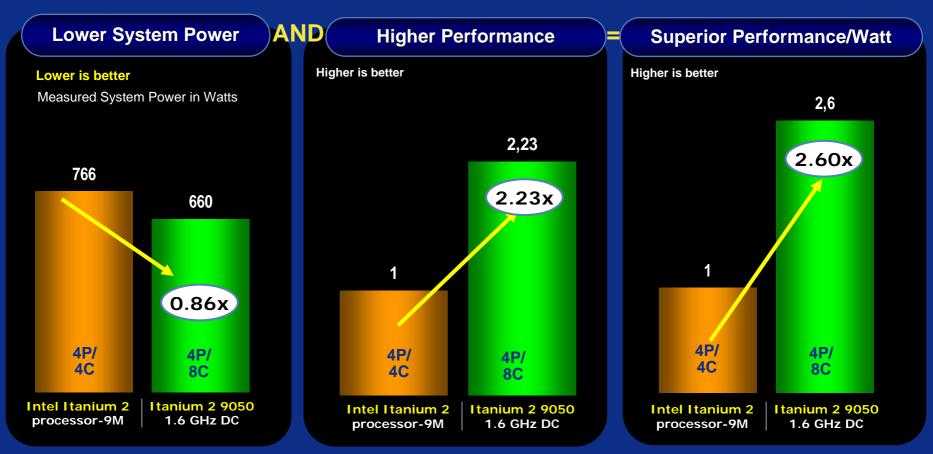

#### Dual-Core Intel® Itanium® 2 processor 9000 sequence server Energy efficiency on STAR-CD\* 3.22

Data Source: Intel internal measurement, See backup for details Itanium 2 9000 sequence: Dual Core Itanium 2 "Montecito 1.6Ghz" "p" is a processor or socket and "C" is a core

Itanium 2 shows 2.6x better performance/watt over Previous generation

#### Agenda

Itanium<sup>®</sup> Processor Family Roadmap

Itanium® 2 Processor update & technology highlights

Montecito Processor Performance update

Itanium<sup>®</sup> 2 Processor Vs Power 5+ competitive

Itanium® 2 Processor Vs X86 Positioning

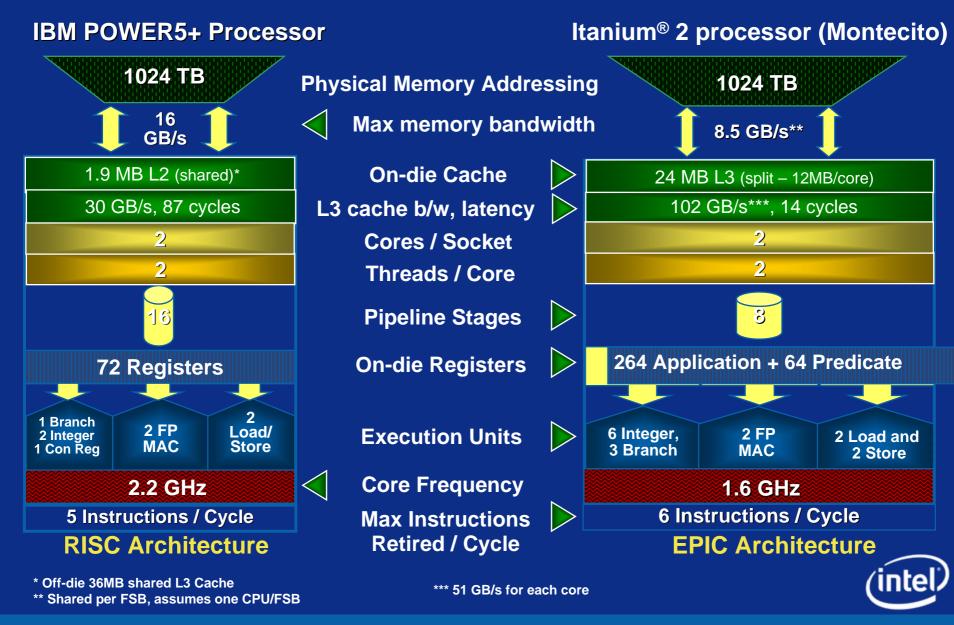

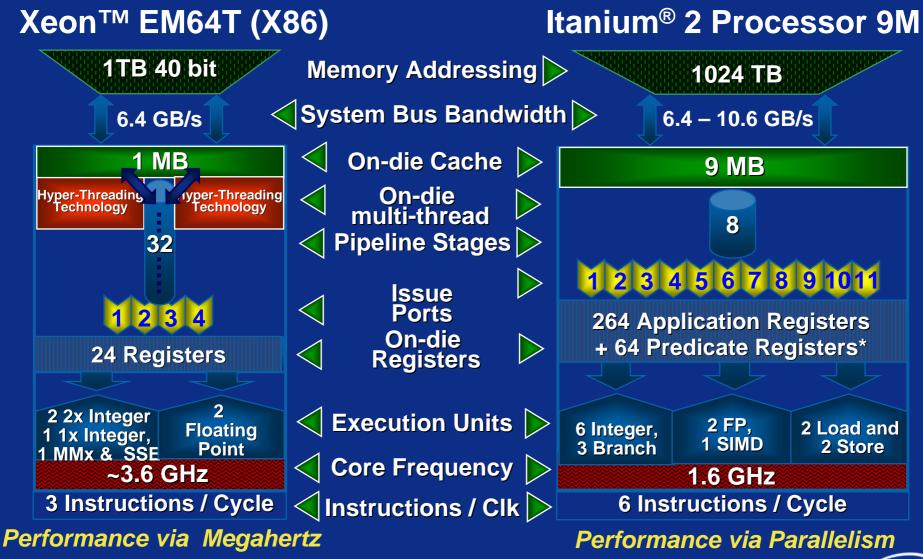

#### High-end microarchitectures comparisons

Rev i1.1\_4718844 In

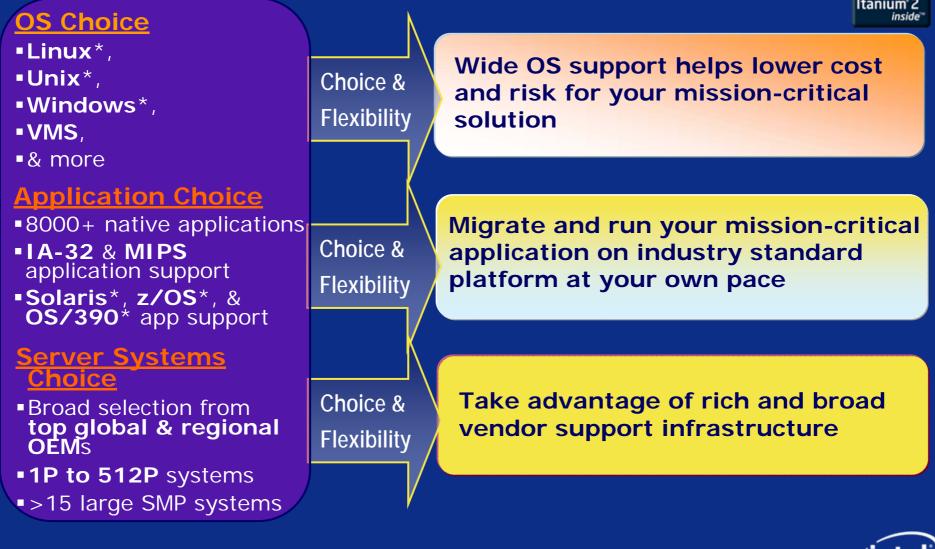

Industry standards-based platform for mission-critical solutions provides choice & flexibility

#### Greater choice helps lower cost and risk

Rev i1.1\_4718844

# New Oracle pricing structure for multi-core processors

| Processor            | Oracles Core<br>Multiplier | Processor             | Number of<br>Oracle licenses |

|----------------------|----------------------------|-----------------------|------------------------------|

| Niagara              | .25                        | Madison               | 1                            |

| AMD / Intel          | .5                         | Montecito (dual core) | 1                            |

| All other Multi-core | .75                        |                       | I                            |

| All Single Core      | 1.0                        | Power5+* (dual core)  | 1.5                          |

#### The Intel Advantage:

•Montecito take the advantage away from Power5+\*

- 1 Montecito (dual core) = 1 Oracle license

- 1 Power5+\* (dual core) = 1.5 Oracle licenses

With the new Oracle pricing structure for multi-core processor Montecito gains the advantage over Power5+\*

#### Agenda

Itanium<sup>®</sup> Processor Family Roadmap

Itanium® Montecito Processor refresh and Recap and technology highlights

Montecito Processor Performance update

Itanium<sup>®</sup> 2 Processor Vs Power 5+ competitive

tanium<sup>®</sup> 2 Processor Vs X86 Positioning

#### Intel's 64-bit enterprise microarchitectures

\* Intel's EPIC technology includes 64 single-bit predicate registers to accelerate loop unrolling and branch intensive code execution.

Rev i1.1\_4718844

## Intel® Itanium®2 or Intel® Xeon®?

For Your Most Critical Data Center Requirements

Scalable Mainframe-class server Ultimate Flexibility & Reliability

**Itanium** 9000 Sequence

RISC / Mainframe Replacement Medium and Large Enterprise

#### To Standardize Your IT Infrastructure

Cost Effective Reliable High Performance Servers

Xeon

7000 Sequence5000 Sequence3000 Sequence

Small, Medium & Large Enterprise Small and Medium Business

#### Summary

- Itanium architecture's strong roadmap delivers investment protection

- Multi-core, virtualization, power management, and enhanced system bandwidth in 2006 with Montecito

- Itanium 2-based platforms deliver outstanding price/performance along with choice that you don't get with RISC

- Itanium<sup>®</sup> = Platform of choice for SQL server Database

- Itanium<sup>®</sup> = Alternative to proprietary RISC platforms

- Itanium<sup>®</sup> = Choice of hardware, OSs and Applications

- Itanium® = RISC/ mainframe class reliability &

scalability & Performance

Other brands and names are the property of their respective owners

## Quiz

1) What Micro-architecture is dual-core Itanium 2 (Montecito) CPU based?

#### EPIC

2) How many threads an 8-way integrity server can support

#### 32 threads

- 3) What is L3 cache memory size in the new dual-core Itanium 2 (Montecito) processor?

24 MB !

- 4). What new technology is used in Montecito Processor to provide advanced Cache reliability?

Intel Cache Safe Technology

## **For More Information**

Intel® Itanium® 2 processor product information

intel.com/products/server/processors/server/Itanium®2/

End-user usage – case Studies, testimonials

intel.com/business/casestudies/prodserv/index.htm

Reference Solutions and configurations guides

www.intel.com/business/bss/products/server/itanium2/index.htm?ii

d=ibe\_server+dss&#DSS

# Thank You

# Questions?

44 20th July 2006 Intel® Itanium® Architecture Update